# LC フィルタの検討に基づく超高効率 インバータの変換効率 99.6%の実現

中崎 智志\*, 伊藤 正悟, 永井 栄寿, 小原 秀嶺, 河村 篤男 (横浜国立大学)

Verification of 99.6 % Efficiency in DC-AC Inverter based on Investigation of LC Filter Satoshi Nakazaki, Shogo Ito, Sakahisa Nagai, Hidemine Obara and Atsuo Kawamura (Yokohama National University)

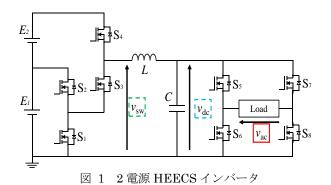

Fig. 1. 2 Battery HEECS Inverter

#### 1. まえがき

近年、電力変換器の超高効率化技術は省エネ分野の重要なテーマとなっている。その中でも数キロワット程度の比較的省電力の DC-AC 変換器は 99.5 %を超える報告例が少ない。ゆえに我々はこの負荷容量の分野において、極限効率の理学的追及を動機として、図 1 のインバータ回路を提案した(1)。本提案回路は、マルチレベル方式を適用した高効率DC-DC コンバータで全波整流波形を生成し、その波形を折り返し回路により正弦波に変換することで DC-AC 変換を実現する。文献(2)では全波整流波形において 99.2 %程度の効率が報告されているが、LC フィルタの設計値に改善の余地が残っていた。

本稿では、本提案回路において高効率化の観点からLCフィルタの検討を行い、改良したフィルタを用いた実験により数キロワット程度のDC-AC変換において99.6 %以上の効率を実測したので、これを報告する。

# 2. 2 電源 HEECS インバータの概要

図 1 に 2 電源 HEECS インバータを示す。前段は 2 電源 HEECS チョッパ(3)の下段にもチョッパ回路を接続した回路 構成の DC-DC 降圧コンバータであり、2 つの電圧源から、任意の直流電圧に降圧できる。出力電圧指令値が  $E_1$ 以下の場合、 $S_3$ は常にオン状態であり、 $S_1$ と  $S_2$ による下段ハーフブリッジ回路で  $E_1$ を降圧する。同様に指令値が  $E_1$ ~ $E_1$ + $E_2$ の場合は、上段のハーフブリッジ  $S_3$ 、 $S_4$ によって  $E_2$ を降圧し、 $S_2$ は常にオン状態となる。

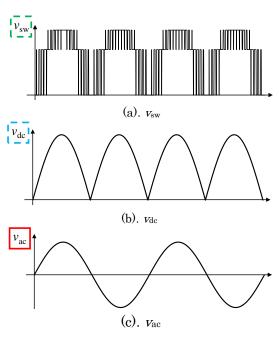

図 2 に各部分での模式的な電圧波形例を示す。図 2(a)は

図 2 各部の模式的な電圧波形

Fig. 2. Voltage waveform at three different points. 全波整流波形を指令値とした PWM 出力電圧であり、LC フィルタを介することで図 2(b)の全波整流波形が得られる。これを全波整流波形状に生成し、後段のフルブリッジの折り返し回路にて極性反転することにより、図 2(c)の通り DC-AC 変換を実現する。

#### 3. LC フィルタの設計値の検討

文献(2)にて設定されている LC フィルタの値では, $80 \, \mu F$  のキャパシタの充放電電流の実効値が定格負荷電流に対して 4 割程度になり,チョッパ部の電流実効値を大きくする要因となっていた。その結果,デバイスおよびインダクタでの導通損が大きくなっていた。本稿では,キャパシタンスを  $8 \, \mu F$  まで小さくし,さらに,出力電圧の THD は 1%程度になるように,ローパスのカットオフ周波数を考慮して LC フィルタを設計した。その結果,インダクタンスを  $2.43 \, mH$  とした。さらに,インダクタの鉄心材料として,(1)ダストコア,(2)フェライト,(3)アモルファスを選択し内部抵抗を十分小さくする条件で,Lを外注製作し,実験を行った。

電源電圧においても従来では出力電圧に対して余剰分を

表 1 実験での回路パラメータ

Table 1. Parameters for experiment.

| Parameter                       | Previous(2)                       | Proposed                          |

|---------------------------------|-----------------------------------|-----------------------------------|

| Output voltage (rated)          | $400  \mathrm{V}_{\mathrm{peak}}$ | $400  \mathrm{V}_{\mathrm{peak}}$ |

| Output current (rated)          | 25 A <sub>peak</sub>              | 25 A <sub>peak</sub>              |

| Load resistance (rated 5KW)     | $16.6\Omega$                      | $16.6\Omega$                      |

| Lower voltage source            | 280 V                             | 280 V                             |

| Upper voltage source            | 140 V                             | 125 V                             |

| Filter inductor                 | 585 μΗ                            | 2.43 mH                           |

| Internal resistance of inductor | $55.6~\text{m}\Omega$             | $6.24~\text{m}\Omega$             |

| Filter capacitor                | 80 μF                             | 8 μF                              |

| ESR of capacitor                | $1.6~\mathrm{m}\Omega$            | $3.5~\mathrm{m}\Omega$            |

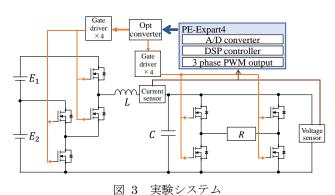

Fig. 3. Experimental circuit.

20 V 設けていたが、本稿では E2 が関与するスイッチング損 を減らす目的で余剰分を5Vまで小さくした。電源電圧比 については文献(2)における仮定の上での最適比を基準とし て設定している。

## 4. 実験での効率測定

2電源 HEECS インバータの効率測定実験を,抵抗負荷を 接続して行った。設定した回路のパラメータを表1に、図3 に製作した実験回路システムを示す。デジタルコントロー ラーとして Myway プラス社の PE-Expart4 を用いた。測定方 法については,2つの直流電圧源および負荷の電圧,電流を HIOKI 社のパワーアナライザ PW6001 にて測定し、効率を 計算した。

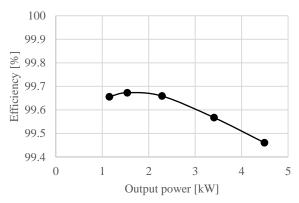

図 4 に 2 電源 HEECS インバータにおける負荷に対する 効率測定の結果を示す。各点 400Vpeak の正弦波を抵抗負荷 に出力しており、横軸は負荷での出力電力である。ただし制 御はオープンループである。DC-AC変換において最高点と して, 1.6 kW 程度の負荷に対し 99.67 %の効率を計測して いる。

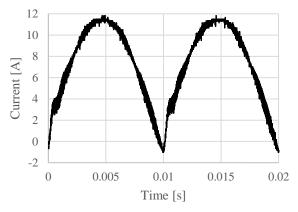

図 5 に一例として,実験での 2.3 kW 程度(99.65%)の出力 におけるインダクタ電流波形を示す。フィルタのキャパシ タに流れる無効電流が小さいため、インダクタ電流は抵抗 負荷の電流によく似た波形を示している。

図 4 DC-AC 変換の効率測定結果

Fig. 4. Measured efficiency of 2 battery HEECS inverter.

図 5 実験でのインダクタ電流 i<sub>L</sub>(R=33.3 Ω)

Fig. 5. Experimental waveform of inductor current.

### 5. まとめ

超高効率な DC-AC 変換回路, 2電源 HEECS インバータ においてさらなる高効率化を目的とした LC フィルタの再 検討を行った。従来と比較してフィルタのキャパシタンス を減らし、インダクタンスを大きくすることで、効率測定実 験では 99.6 %台の DC-AC 変換効率を達成した。 損失の詳細 な分析に関しては別の機会に報告する。

本研究の一部は、日本学術振興会科学研究費補助金基盤 研究(S)(課題番号:17H06147)によって行われたことを記す と共に, 関係者各位に謝意を表す。

- 秀嶺, "部分電力変換の原理に基づく (1) 河村 - タ実現の理学的追求", 平成30年電気学会全 高効率インバー 国大会, 2018

- (2) A. Kawamura, S. Nagai, S. Nakazaki, S. Ito and Hidemine Obara, "A very High Efficiency Circuit Topology for a few kW Inverter based on Partial Power Conversion Principle", in Proc. of 2018 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 1308-1313, Sept. 2018.

- (3) Y. Tsuruta and A. Kawamura, "Principle Verification Prototype Chopper using SiC MOSFET Module Developed for Partial Boost Circuit System", in Proc. of 2015 IEEE Energy Conversion Congress and Exposition (ECCE), pp.1421-1426, Sept. 2015.